1. はじめに

このドキュメントは Nexus 9000 のハードウエアアーキテクチャのコンポーネントであるスライス (Slice) について解説します。

2. 概要

Nexus 9000 シリーズでは弊社で設計したカスタムシリコンを採用しています。

最初は汎用シリコンと併用でしたが、EX シリーズ以降はカスタムシリコンのみが搭載されています。

このカスタムシリコンは SoC (System on Chip) で、MAC や Forwading Controller、Slice のインターコネクトを含みます。

SoC 内部で MAC や Forwording Engine を統合した一つの集合をスライスと呼んでいます。

3. Nexus 9000 シリーズに搭載されているカスタムシリコンについて

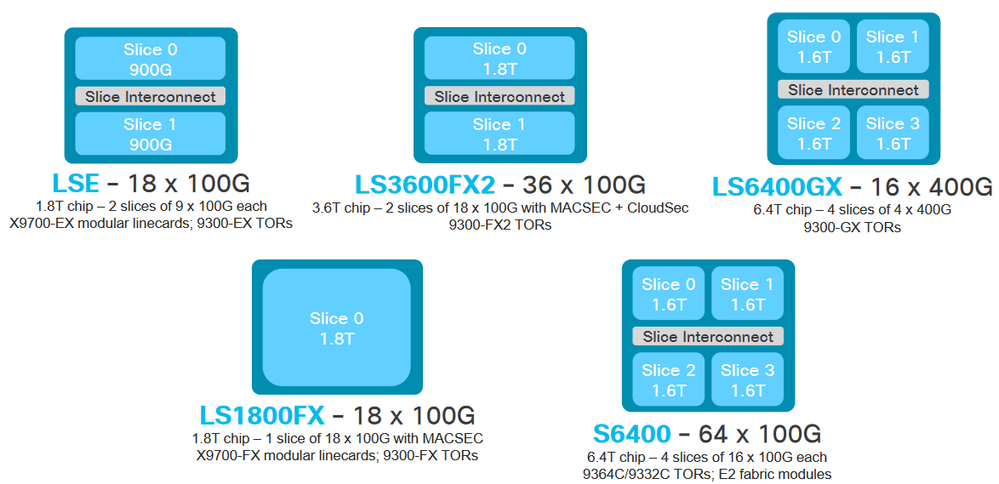

Nexus 9000 シリーズのリリース以降以下のようなカスタムシリコンが使用されています。製品名とリンクしたカスタムシリコンが使用されています。

4. スライスの実装

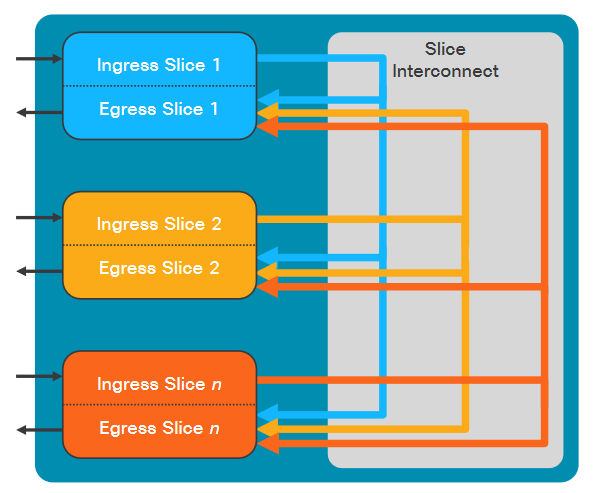

スライス内部では入力用 (Igress Slice) と出力用 (Egress Slice) で機能がそれぞれ分けられ、カスタムシリコン内に複数の Slice がある場合は Slice Interconnect を経由してパケットの転送が行われます。Slice Interconnect はどの Slice 間も Non Blocking となっており、ここで通信が詰まるといったことはありません。

これは Nexus 5000 シリーズの SoC と Fabric Interconnect と同様の関係になります。

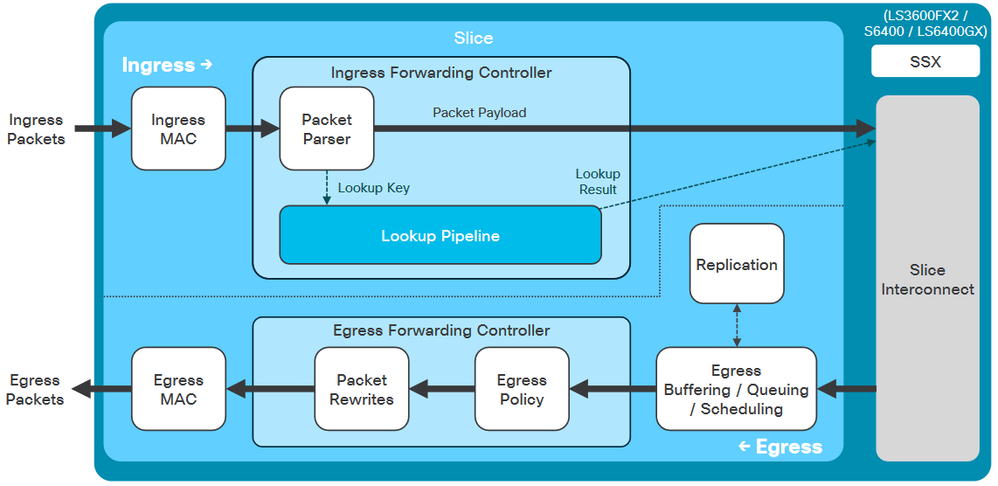

Ingress Slice には MAC とForwading Controller、Egress Slice には Buffer/Queuing/Scheduling、Forwading Controller、MAC が含まれます。

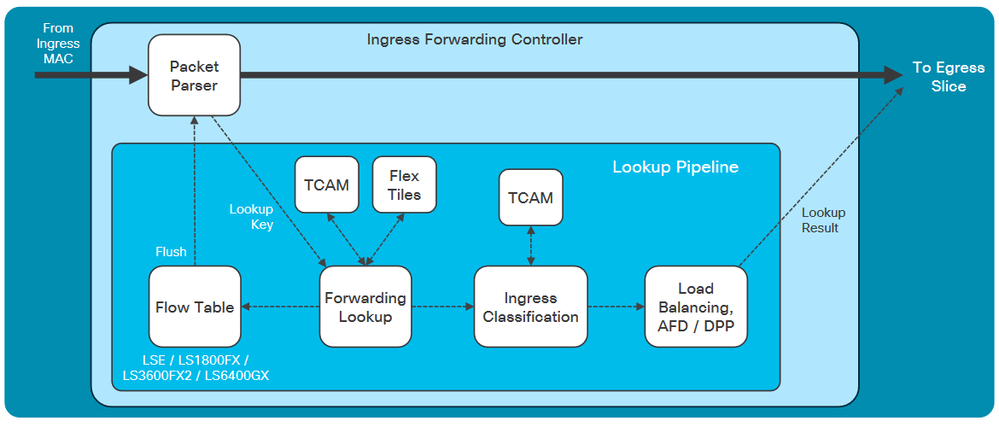

Ingress Forwarding Controller にはこれまでの Nexus シリーズの Forwarding Engine と同様の機能が備わっています。

転送系のトラブルシューティングを行う際は、以上の実装を踏まえてスライスとポートの関係も意識しながら作業を進める必要があります。

5. Slice を確認するコマンド

以下のようなコマンドでポートとスライスの紐づけを確認する事が可能です。

5.1. show hardware internal tah interface [all|ethernet x/y]

全てのポート,もしくは任意のポートについて確認できます。

n9k_switch# show hardware internal tah interface ethernet 1/1

#########################################

IfIndex: 0x1a000000

DstIndex: 6144

IfType: 26

Asic: 0

Asic: 0

AsicPort: 16

SrcId: 32

Slice: 0 <<<< E1/1 は Slice 0 に所属

PortOnSlice: 16

Table entries for interface Ethernet1/1

PifTable:

ENTRY: 32

default_vlan : 1

=========================================

NIV_INDEX not found in pif_table. Check if port is up

5.2. slot [x] show hardware internal tah all-front-ports

Nexus 9500 シリーズの場合にはラインカードのスロット番号、Nexus 9200/9300 シリーズでは "slot 1" を指定します。attach module 後に show 以降を入力する方法もあります。

n9k_switch# slot 1 show hardware internal tah all-front-ports

For front port 1

Inst| slice|MAC serdes|asic_port_num|Speed/Type|MTU src_id|sbuss_add|FEC TX-pre-post-attn-Pol|RX-Pol

State

========================================================================================================================

================

0| 0x0| 4 1| 16| 10G/Fixed|Auto 0x632 32| 533|N/A 3=10=4=0|0

DISABLED

Inst HW-TX-pre-post-attn-Pol RX-Pol FEC MTU IPG State

=========================================================================

0 3=10=4=0 0 0 0x632 0xc DOWN

*****End of port information*****

For front port 2

(snip)

6. 関連コンテンツ

7. 参考資料