- Cisco Community

- Technology and Support

- Networking

- Switching

- Re: what is a rx ring/tx ring in router?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

05-18-2010 07:04 PM - edited 03-06-2019 11:09 AM

hi all

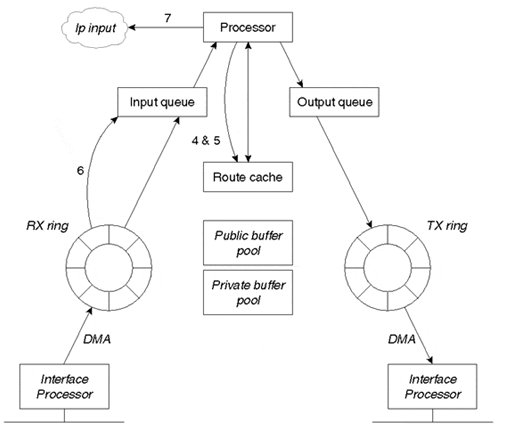

below image describes a process router routes/switches a packet.

first router receives a packet

interface processor stores the packet private buffer or public buffer.

above step.

what's a role of RX ring?

ring is a shared memory(buffer) or a dedicated memory(buffer) for interface?

is there anyone what is a rx ring(tx ring)?

Solved! Go to Solution.

- Labels:

-

Other Switching

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

11-18-2011 02:08 AM

Hi,

I would like to add a little more.

Along with public and private interface pools, Cisco IOS creates special buffer control structures called rings. Cisco IOS and interface controllers use these rings to control which buffers are used to receive and transmit packets to the media. The rings themselves consist of media-controller-specific elements that point to individual packet buffers elsewhere in I/O memory.

Each interface has a pair of rings - a receive ring for receiving packets and a transmit ring for transmitting packets. The size of the rings can vary with the interface controller. In general, the size of the transmit ring is based on bandwidth of the interface or VC and is a power of two (Cisco Bug ID CSCdk17210).

Regards,

Kevin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

11-18-2011 03:15 PM

Hello,

In addition to all answers by other friends here, the term ring in general describes a circular buffer, i.e. a formerly linear list of entries in which each entry has a pointer to the next element in the list, and the "last" element points back to the "first" element in the list, thereby making it circular.

Hence, a ring has a finite space - it can contain a limited number of entries. In addition, entries are added sequentially into a ring, and if the ring has the maximum size of N elements, adding the (N+1)th element will place it on the 1st place, essentially replacing the former 1st entry. In other words, a ring of size N always holds at most N most recent entries. This is especially interesting for congestive applications like interface buffers, in which a transient burst may cause the interface buffers to overfill. In such case, these buffers will keep at most N most recently received frames.

Also, the Tx/Rx rings are often implemented in hardware, as a part of an interface controller. These controllers have buffers to store excessive received or transmitted frames, and the buffers are circular in nature - with limited space, and if overfilled, the most recent entry overwrites the least recen. What you are seeing in your exhibit are most probably the HW rings implemented inside a particular interface type.

Best regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

11-19-2011 05:09 AM

Disclaimer

The Author of this posting offers the information contained within this posting without consideration and with the reader's understanding that there's no implied or expressed suitability or fitness for any purpose. Information provided is for informational purposes only and should not be construed as rendering professional advice of any kind. Usage of this posting's information is solely at reader's own risk.

Liability Disclaimer

In no event shall Author be liable for any damages whatsoever (including, without limitation, damages for loss of use, data or profit) arising out of the use or inability to use the posting's information even if Author has been advised of the possibility of such damage.

Posting

Just to add a bit to what the other posters have already noted. What's "special" about the ring buffers they are designed to try to keep up with the interface traffic requirements, especially when receiving. Usually they are tied to hardware interrupts. The reason they are "circular" is because often they use an address block and modulus address offsets, often binary. For example, if you allocated 3 bits for an address offset you would have 8 offsets, zero to seven. All you need to do is increment the offset. When it overflows it wraps back to the beginning, hence its a circular or ring buffer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

05-18-2010 07:13 PM

Hi!

Well .. Im not very expert about this thing.. but I Know that..

RX = Receive Traffic

TX = Transmit traffic

I think that the "ring" is a simbol to refer about series of tasks inside a queue...

Im not pretty sure... Experts... what are your opinions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

05-18-2010 07:36 PM

Thanks for your reply

i guess ring is a kind of buffer or memory.

but i don't know which type of buffer?

i think that is one of above two

Ring is

1. buffer asigned for only h/w interfae(it means that only the H/W interface can use the buffer)

2. buffer asigned among a shared buffer by scheduling of ios

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

11-18-2011 02:08 AM

Hi,

I would like to add a little more.

Along with public and private interface pools, Cisco IOS creates special buffer control structures called rings. Cisco IOS and interface controllers use these rings to control which buffers are used to receive and transmit packets to the media. The rings themselves consist of media-controller-specific elements that point to individual packet buffers elsewhere in I/O memory.

Each interface has a pair of rings - a receive ring for receiving packets and a transmit ring for transmitting packets. The size of the rings can vary with the interface controller. In general, the size of the transmit ring is based on bandwidth of the interface or VC and is a power of two (Cisco Bug ID CSCdk17210).

Regards,

Kevin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

11-18-2011 03:15 PM

Hello,

In addition to all answers by other friends here, the term ring in general describes a circular buffer, i.e. a formerly linear list of entries in which each entry has a pointer to the next element in the list, and the "last" element points back to the "first" element in the list, thereby making it circular.

Hence, a ring has a finite space - it can contain a limited number of entries. In addition, entries are added sequentially into a ring, and if the ring has the maximum size of N elements, adding the (N+1)th element will place it on the 1st place, essentially replacing the former 1st entry. In other words, a ring of size N always holds at most N most recent entries. This is especially interesting for congestive applications like interface buffers, in which a transient burst may cause the interface buffers to overfill. In such case, these buffers will keep at most N most recently received frames.

Also, the Tx/Rx rings are often implemented in hardware, as a part of an interface controller. These controllers have buffers to store excessive received or transmitted frames, and the buffers are circular in nature - with limited space, and if overfilled, the most recent entry overwrites the least recen. What you are seeing in your exhibit are most probably the HW rings implemented inside a particular interface type.

Best regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

11-19-2011 05:09 AM

Disclaimer

The Author of this posting offers the information contained within this posting without consideration and with the reader's understanding that there's no implied or expressed suitability or fitness for any purpose. Information provided is for informational purposes only and should not be construed as rendering professional advice of any kind. Usage of this posting's information is solely at reader's own risk.

Liability Disclaimer

In no event shall Author be liable for any damages whatsoever (including, without limitation, damages for loss of use, data or profit) arising out of the use or inability to use the posting's information even if Author has been advised of the possibility of such damage.

Posting

Just to add a bit to what the other posters have already noted. What's "special" about the ring buffers they are designed to try to keep up with the interface traffic requirements, especially when receiving. Usually they are tied to hardware interrupts. The reason they are "circular" is because often they use an address block and modulus address offsets, often binary. For example, if you allocated 3 bits for an address offset you would have 8 offsets, zero to seven. All you need to do is increment the offset. When it overflows it wraps back to the beginning, hence its a circular or ring buffer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

11-27-2011 09:41 PM

Hi all

Thanks for reply.

your explanation are very helpful and clear to understand it.

thanks again and have a nice week!!!

Best regards,

Sanghee

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

07-14-2013 08:31 AM

Hi, I know this thread is quite old but could someone tell me where is it possible to find this or similar diagram and where I can find more information about cisco routers hardware queueing mechanisms (especially 2600 platform). I need it for my dissertation project.

Thanks in advance

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

07-14-2013 11:37 AM

Hello Luke,

These links may be of some interest although I am not sure if they cover all necessary details:

http://www.cisco.com/en/US/products/hw/routers/ps259/products_tech_note09186a0080094e92.shtml

http://www.cisco.com/en/US/products/hw/routers/ps133/products_tech_note09186a00800a7b80.shtml

http://www.cisco.com/networkers/nw99_pres/601.pdf

Some interesting information can also be found in the Cisco Press book called Inside Cisco IOS Software Architecture - you will find many references to it on Google.

Best regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

07-14-2013 11:43 AM

Hi Peter,

I've seen all the links but not the book so thanks for your help.

Discover and save your favorite ideas. Come back to expert answers, step-by-step guides, recent topics, and more.

New here? Get started with these tips. How to use Community New member guide